1.3.5 – FP6000 Processor Data Flow

This extract from the April 1963 visit report details the dataflow of the FP6000 processor being recommended for adoption. It later became the ICT 1904.

Data Flow

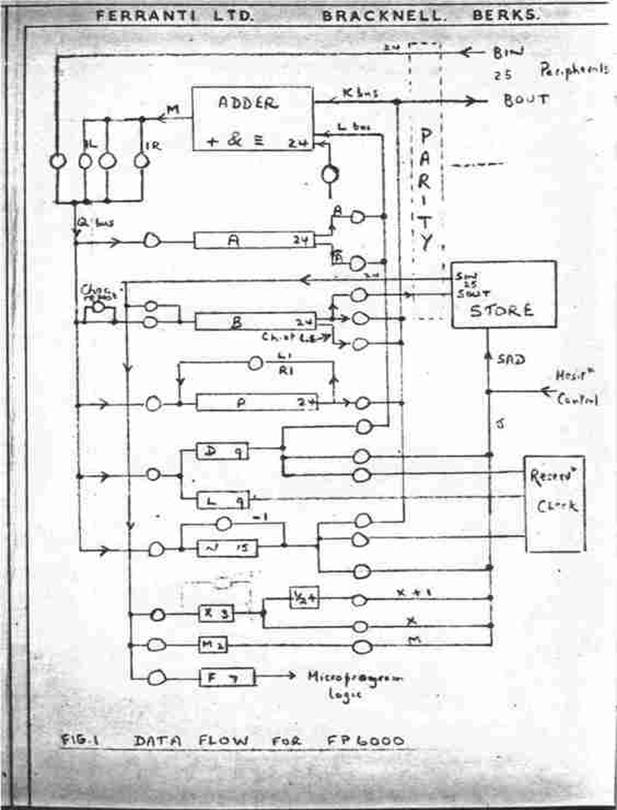

General – The above figure shows the main FP6000 data flow which is relatively straightforward. One unusual feature is the dumping of the order number register P into store during all double length operations (including multiply, divide and floating point).

Briefly the data flow consists of a mill (+, &, ≠) with 2, 24 bit parallel input highways and one 24 bit output highway. The latter emerges via a shift facility (0, +1,-1). The accumulators are not external but held in the core store. The L input highway serves A, a 24 bit working register with output complementing facility for subtraction, D, a 9 bit register holding the datum for that programme (see time sharing below). The K input highway serves B, the core store data register, P, the order number register which is also used for double length numbers and N, a 15 bit register holding the store address. P has a shifting facility (+1,-1) for use in multiplication and division.

Store

addressing and data

The store is addressed for instructions, operands (N), accumulators (X) and modifiers (M) all relative to the datum D for that programme which is added to all N addresses but ORed to X and M (See below). A further facility is provided for addressing the store with X+1 for double length quantities. Data into and out of the store is via the B register which is actually the store data register. The latter is not part of the memory as is usual. This assists considerably in simplifying store expansion. Similarly, N, is the store address register. All data transfers to and from store are checked by a 24 bit parity generator/ checker which also checks peripheral transfers over the standard interface.

Multiprogramming

(Time Sharing)

A hardware facility provides a reservation check that the address N (modified by M if required) is less than or equal to L and adds the datum B to N. This ensures that all store accesses lie between D and D+L. D and L are set by the EXECUTIVE (Supervisor). Both D and L are modulo 64.